In the previous couple of articles, I talked about Lattice FPGAs. Let's talk today about effective development for them. One of our major managers assures that from conversations with foreign customers, he found out that Russian developers are considered to write cool things, but do it extremely slowly. Well, of course, compared to developers from other countries. And of course, “cool” comes first.

One method to get around the problem of development speed is to use ready-made infrastructure for projects. I did a series of articles about the Redd complex, where I promoted the use of ready-made bus infrastructure in the Quartus development environment. At first it was an honest processor system, then we removed the processor and left the buses.

The list of articles in this series is below the cut.

1. Development of the simplest “firmware” for the FPGA installed in Redd, and debugging using the example of a memory test 2. Development of the simplest “firmware” for the FPGA installed in Redd. Part 2. Program code 3. Development of a custom kernel for integration into an FPGA-based processor system 4. Development of programs for the Redd central processor using the example of access to the FPGA 5. First experiences in using the streaming protocol using the example of CPU-processor communication in the Redd FPGA complex 6. Merry Quartusel, or how the processor came to such a life 7. Code optimization methods for Redd. Part 1: cache impact 8. Code optimization methods for Redd. Part 2: non-cacheable memory and parallel operation of buses 9. Extensive code optimization: replacing the clock generator to improve system performance 10. Access to Redd complex buses implemented on FTDI controllers 11. Working with non-standard Redd complex buses 12. Practice in working with non-standard ones buses of the Redd complex 13. Forwarding USB ports from Windows 10 for remote work 14. Using a Nios II processor system without a Nios II processor core 15. Practical work with FPGAs included in the Redd kit. We master DMA for the Avalon-ST bus and switching between Avalon-MM buses

Then I did a couple of cycles where I actively used this approach. I only had to add problem-oriented modules; the development environment created the rest for me.

Cycle about logic analyzer - under the cut

- Development of a simple logic analyzer based on the complex

- ReddDevelopment of a logic analyzer based on Redd - testing its operation in practice

- Making the head of a USB bus analyzer based on the Redd complex

- We simulate the behavior of a Quartus project in Verilog in the ModelSim environment

- Modeling firmware in the ModelSim environment using models in the SystemC language

- We simulate the system to check the functionality of the USB analyzer head

- Practical experiments with a Redd-based USB analyzer

And under this cut is a cycle about the USB bus analyzer

1. We begin experiments with the USB 3.0 interface through the FX3 family controller from Cypress 2. We finalize the USB 3.0 firmware using the SignalTap analyzer built into the Quartus 3 development environment. We learn to work with a USB device and test system made on the basis of the FX3 controller 4. We deal with timeouts when using USB 3.0 via the FX3 controller, which arise under certain conditions 5. We add support for Vendor commands to a USB3.0 device based on FX3 6. We make an SPI to AVALON_MM block for a USB device based on FX3

Is there something similar for Lattice in particular and the Yosys/NextPNR coupling in general? You will not believe! Not only does the solution exist, but it is also so cross-platform that it is suitable for Yosys/NextPNR, Quartus, and Vivado! And it's called Litex. So, let's try to experiment with it for the approach that I have been promoting for a long time: “make a standard base, and string your target blocks onto it.” And who knows what Litex is - don’t be scared! We will make our blocks on Verilog!

Introduction

The first thing that needs to be said about Litex is that everything is done there in Python. But I was still not familiar with this language. But overall, the basics were enough to get started.

Further, if you try to read the manuals on this system, you will find statements that you don’t need to do anything in Verilog, everything can be described in Python. Even the modules themselves. Yes, you can. But if you compare the volume of code, its readability, and most importantly, the number of things that need to be kept in mind, in my opinion, this approach is much inferior to direct development on Verilog. So don't worry, I won't teach this.

What Litex does well is create a basic bus-centric system. Standard controllers have already been developed for it: SDRAM, UART, I2C, SPI, and many others. It can use Wishbone as a base bus, so many cores from the OpenCores.org website can be installed on this system (I just participated in a project where this was done). So we will use this useful property.

Further, the database of this environment already contains a lot of ready-made boards based on Altera (Intel), Xilinx and Lattice. Therefore, our developments will be cross-platform, because, in principle, we will be able to switch the top level from one board to another, without really looking closely at which company’s FPGA is there. The top level was created for us exactly for the FPGA that we specified. Taking into account its specifics! If only it was in the Litex base, and the base there is gorgeous.

And within the board, the legs have already been described in groups. Let's say there is a group of SDRAM. There are groups “connector J1” and so on. When compiling a project, it is enough to specify the board version so that the pinout we need is automatically connected. So we describe our project in end-user abstraction. The end user sees a connector on the diagram... Well, let's say J15. So it connects to his legs! And how everything is routed on the board should not interest him.

In general, we use everything that is useful and do not use what seems useless to us. Yes, we will have to write a little in Python. But when working with Quartus, we also created strange files, it’s just that the GUI environment helped us with this. And so – the connectives were also written in a strange language.

In my mind, it would be necessary to build a large series of lectures, smoothly introducing the course. The lectures would have gotten interesting from the third or fourth... But after the great failure with the series of articles about Teensy, I no longer plan to go further than one article ahead. It's a shame to spend a lot of energy on something that is actually not in demand. Therefore, we will start right away with the interesting things, violating some academic principles. But you don’t have to keep a bunch of articles in your desk that you wasted your energy on, knowing at the same time that few people will need them, as was the case with Tinsey. It's better to spend your energy on something else. Therefore, I will just briefly talk about the types of connections to the bus, and we will immediately rush into battle. We will make the system completely spartan, but then we will find out how to add auto-documentation to it... Or we won’t find out... But then.

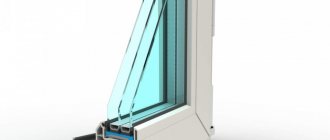

PROPLEX OUTLINE profile

This system of two-chamber profiles is intended for glazing balconies and loggias of residential buildings, summer houses, industrial premises and non-residential buildings.

The two-chamber profile in terms of heat transfer resistance (0.405 m2 0C/W) and strength of corner welded joints (frame - 1000N, sash - 1350N) meets the requirements of GOST 30673-99 and SNiP 02/23/2003 for translucent enclosing structures (Test Report No. 27- 11/051/1 dated December 23, 2005).

The Proplex Outline PVC profile, in addition to superior price, has a number of advantageous features from PVC and aluminum systems. Thus, PVC profiles retain heat better and provide better sound insulation compared to aluminum profiles. PVC profiles are less susceptible to mechanical damage (scratches) than aluminum ones, both during processing, transportation, installation, and during subsequent everyday use.

The profile can be used to mount glass, single- and double-chamber double-glazed windows up to 22 mm. Linings under double-glazed windows ensure optimal distribution of loads on the end of the double-glazed window, and weather- and wear-resistant seals prevent water from penetrating into the rebate of the double-glazed window. The edges of the profile are rounded. Water does not linger on the ledges and flows down easily.

The frame, sash and impost are reinforced with metal liners. This allows the structure to withstand wind loads and prevent the sash from sagging under the weight of the double-glazed windows.

Condensate is drained along the inclined part of the profile rebate, and water drainage in the frame is provided by drainage holes that can be hidden with drainage covers.

Buses and command-status registers

When developing for Altera, I always connected to the Avalon-MM bus, or sent streams via the Avalon-ST bus. Here we can also connect our devices to the Wishbone bus. But in addition to this, we are given the opportunity to create our own command and status registers (aka Command Status Registers, aka CSR).

In Alter's projects, I had to create these registers myself, decode the address of the command register, the address of the status register on the bus, and compare the entities of the Verilog code with these registers myself. Automation can do everything for me right away.

That is, I take the simplest Verilog module. Let's say this:

module gpu( input clk, output hsync, output vsync, output color, input [15:0] x0, input [15:0] x1, input [15:0] y0, input [15:0] y1);

clk line must come from somewhere in the clock generator

The color , hsync , vsync lines must clearly go to the FPGA legs, since they will go into the video connector (in our case, into VGA).

And the lines x0, x1, y0 and y1 are control inputs that specify the coordinates of the rectangle drawn on the screen. They must be installed along the bus.

And so, in order not to remake such a module to work with the Wishbone bus (and tomorrow we may even need AXI), we can easily connect x0, x1, y0 and y1 to the CSR lines. Since this is much simpler than implementing the work with the bus ourselves, let’s start with this. Let's turn the long-suffering Colorlight 5A‑75B board into a VGA adapter using Verilog code found on the Internet. This code just generates a VGA signal. It’s just a pity that such a video card won’t be able to mine. True, first we need to install the same Litex with which we will do everything.

Advantages of NewTek doors and windows

Profile NewTek SY 68

Aluminum is an excellent material for the manufacture of profile structures. With its low weight, it has high strength and durability. Thanks to their stylish and discreet design, windows and doors made of “warm” aluminum are in demand in administrative buildings and are often installed in commercial real estate, the residential sector, and educational institutions.

| Specifications | |||

| Material of manufacture | EN AW 6060 T66 anodized aluminum | ||

| Sash weight 2 hinges / 3 hinges | 150 kg/ 180 kg | ||

| Frame/sash profile width | 60mm / 68mm | ||

| Heat loss | 0.35 m.sq.*°C/W | ||

| Glazing thickness | up to 40 mm (up to 36 mm recommended) | ||

| Shelf under glass | 22 mm. | ||

| Window calculator from NewTek 68 profile | Window calculator | ||

Advantages of a “warm profile”

- Perfectly flat, smooth surface without flaws;

- Resistant to dirt and easy to maintain;

- Security against unauthorized entry;

- Rigid reinforced contour and stable geometry;

- Versatility - it is suitable for creating Newtek doors, stained glass windows, entrance lobbies;

- Can be installed even in cold climates;

- Attractive and stylish design, including the possibility of painting according to the RAL table.

Installing Litex

Installing Litex is not easy, but very simple. This is equally easy to do on Windows and Linux. First we install Python. There is no way without him. Next, go to the project page: enjoy-digital/litex: Build your hardware, easily!, there are instructions there. It is enough to download and run one single Python script. Just keep in mind that it will pump up a bunch of directories one hierarchy level above itself. Here is this file on my machine:

As we can see, he lives at level D:\LATTICE\Litex\litex

Now look what he did on level D:\Lattice\Litex! Before installation there was only one litex directory:

Keep in mind! Otherwise, you will have to clean the directory later... I cleaned it...

That's it. So that the article does not grow too much, let’s finish the theory and start practicing. There will be a lot of it.

Creating a project

All the guides that I could find are aimed at both Python and Litex specialists. Everything is shown there in general terms. Like, we rule this like this, this is like this, this is like this... Aha! And I’m sitting there, staring like a sheep at the new gate, and I don’t understand what the authors had in mind! So let's look into everything in detail.

Let's start with the source of inspiration. I found the best example here: https://gist.github.com/hinzundcode/129d0f81fe24257240d55401f04cdb5a

True, there is only one output for all three signals: R, G and B. But today we will simply connect it to one line. Well, let's say, to the green one. We'll redo it sometime later, today we won't complicate anything, we'll use ready-made solutions.

So. Let's start making our project. To do this, launch Visual Studio (of course, it must have Python support enabled) and create a new project. Looking for a Python template:

And in the resulting list, select Python:

I chose the project name mypytest , and I also chose a simpler location path. The rest was left as default.

That's it, let's create a project. Ufff. And what should I write there? We go to the directory where Litex was installed and open litex-boards there. It contains litex_boards. And there the most interesting directories are platforms and targets. In both directories there are files whose name reminds us of the name of our board:

The platforms describe everything about our board. Moreover, it describes not just our board, but its different versions. I have already noted that the FPGA pinout is completely different in different versions. Thanks to this description, we can select the board and version through the options for the Python script, and the system will automatically select the pin numbers. We'll use this soon. But first we'll go to the targets directory. This is where the target system is described. Let's take a look at the \Litex\litex-boards\litex_boards\targets\colorlight_5a_75x.py file. It consists of two large parts. The first part describes the classes. Namely, the class of clock domains _CRG and the class of the base platform BaseSoC . We can easily use these base classes, although we can write something of our own in the image and likeness. We will write our own when we become cool. There is already too much new information for us now. So we will use the ready one.

The following is a description of the main() . This is what we need to copy to our file, which we created in Visual Studio.

Proplex window systems

PROPLEX is the first Russian developer and largest manufacturer of PVC window systems using Austrian technologies. The plant for the production of PVC window profiles and window sills was built in 1999 in the Moscow region.

The enterprise is equipped with modern equipment from engineering companies from Austria and Germany.

Proplex pays special attention to the selection of raw materials and components, using materials from leading suppliers from Austria, Germany, France, Russia and the USA in production.

Proplex system of plastic profiles is designed for the manufacture of all types of windows and doors of any premises and is specially adapted to Russian operating conditions.

All Proplex comply with the requirements for plastic windows for thermal insulation, as well as all modern international standards. Windows from the Proplex are recommended for installation in children's, preschool and medical institutions (appendix to the certificate of conformity No. ROSS RU.SL08.N00097 FROM 12/15/05);

Today, Proplex has the largest network of its own regional ones in the Russian Federation, which allows it to ship products in the shortest possible time. Since 2000, more than 17 million Proplex .

Brief technical characteristics of the Proplex 58 profile

- Profile installation width: 58 mm

- Number of profile cameras: 3

- Glazing thickness: 24 mm (single-chamber) - 32 mm (double-chamber)

- Height of the outer wall of the glass unit: 2.7 mm

- Reduced heat transfer resistance (max.) - 0.64 (with amplifier), 0.75 (without it) m2 ° C / W

- Tightness - class A

- Service life - up to 60 years.

- Products are certified

Peculiarities

- The appearance of the profile is designed in a modern style. The profile in the mass is milky white with a semi-matte (non-glare) surface.

- Profile production is controlled by a specially developed quality assurance system. It includes both control of the production process itself (incoming quality control of raw materials, control at various stages of the technological process, control of finished products - a total of 21 inspection points), and quality assurance subsystems for all service processes.

- The design of the bead ensures stepless interfacing with other profiles (dirt does not accumulate at the joint.

- Special grooves on the hidden surfaces of the profile facilitate the fastening of fittings and reinforcing liners, preventing the screws from being torn off and accurately marking the attachment points.

- Optimal price compared to imported analogues.

Brief technical characteristics of the Proplex Comfort profile

- Profile installation width: 70 mm

- Number of profile cameras: 4

- Glazing thickness: 24-32 mm (single-chamber), 32-40 (double-chamber)

- Height of the outer wall of the glass unit: 2.7 mm

- Reduced heat transfer resistance (max.) - 0.69 (with reinforcing amplifier) and 0.79 (without it) m2 ° C / W

- Tightness - class A

- Fittings system -12/20-9

- Service life - up to 60 years.

- Class for resistance to climatic influences (according to GOST 30673-99) - frost-resistant version.

- Service life - up to 60 years. Products are certified

Peculiarities

- The appearance of the profile is designed in a modern style. The profile in the mass is milky white with a semi-matte (non-glare) surface.

- A mixture composition developed specifically for Russia is used. Proplex profiles are recognized as frost-resistant profiles and are recommended for installation in any climatic zones of Russia, including in the Far North

- Compared to three-chamber profiles, windows from the Comfort provide better heat and noise protection, and compared to five-chamber profiles - a better price.

First modifications of the project

So. We copied everything starting from the line

def main():

and until the end of the colorlight_5a_75x.py file into your project. Can I run it for testing? Not really.

The first thing to do is to figure out what Python we are using. I had Python 3.7 on my machine, which was installed along with Visual Studio, as well as Python 3.10, in which the Litex environment was installed. Of course, from under the Studio everything tried to run under version 3.7, but nothing like that was installed there. And nothing worked. Therefore, select the menu item Tools->Python->Python Environments :

And in the window that appears, select the version under which Litex was installed. And then on my screenshot it says: “This is the default environment for new projects.” And if a different version is selected, at this point you will be asked to make this version the default tool. I took advantage of it.

Now we need to set several options for starting the project. After all, when you run a program in Python, keys with options are passed to the script. We need to ask them here too. To do this, select the menu item Debug->Debugging properties for the project :

And there I went to the “Layout” tab and entered the keys that add an Ethernet-Wishbone bridge to the system and set the IP address of my board on the Ethernet bus.

--with-etherbone --eth-ip=192.168.2.128

Ufff. Environment preparation is complete. Python specialists nervously knock on the monitor and shout that it’s too early to start, but I don’t want to convey to the reader “Remember and repeat.” I want the reader to learn to understand the dialogue with the system, what is worth adding. So let's run the code! And immediately we get an exception

Remember how you have to struggle with #include ? Now we will also suffer a little. First of all, add the line at the very beginning of the file:

from migen import *

She will have to be remembered. She is the basis of everything! If anything, Migen is Litex's maiden name.

But then - you can already deduce something experimentally. Remember I showed two extremely important files with the platform and the target system? They need to be turned on. And here's what's surprising. Let's look at the path to the first file:

We need to enter the path relative to the root for Litex. Moreover, in Visual Studio IntelliSense will be at our service. Let's start writing:

Do you see? They are already starting to give us hints. Let's select litex_boards, press the dot - they will prompt us further

This is how we easily and naturally import everything we need from those very useful two files. And the first three lines of our file will be:

from migen import * from litex_boards.targets.colorlight_5a_75x import * from litex_boards.platforms.colorlight_5a_75b import *

Wonderful! We try to start... We get this disgrace

What kind of toolchain is this? What kind of compiler is this? The fact is that by default, they are trying to add a processor core to our system. But today we don’t need it. We only need a bus with devices on it. the Ethernet to Wishbone bridge , which we recently added in the options. Let's ditch the processor.

We abandon the processor core

In short, here we need it:

soc = BaseSoC(board=args.board, revision=args.revision, sys_clk_freq = int(float(args.sys_clk_freq)), with_ethernet = args.with_ethernet, with_etherbone = args.with_etherbone, eth_ip = args.eth_ip, eth_phy = args. eth_phy, use_internal_osc = args.use_internal_osc, sdram_rate = args.sdram_rate, **soc_core_argdict(args) )

Add a couple of options at the end. To make it work:

Same thing with text.

soc = BaseSoC(board=args.board, revision=args.revision, sys_clk_freq = int(float(args.sys_clk_freq)), with_ethernet = args.with_ethernet, with_etherbone = args.with_etherbone, eth_ip = args.eth_ip, eth_phy = args. eth_phy, use_internal_osc = args.use_internal_osc, sdram_rate = args.sdram_rate, cpu_type = None, cpu = None, **soc_core_argdict(args) )

But we agreed that I teach you how to do everything in dialogue with the system. Therefore, I begin to justify it. In this article, Experimenting with FPGAs of the ECP5 family from Lattice / Habr (habr.com), I already provided a link to the enjoy-digital/colorlite project: Take control of your Colorlight FPGA board with LiteX/LiteEth (github.com). In it, the authors achieve work without a processor core. How? Let's look at the target system class that we use:

class BaseSoC(SoCCore):

And this is how it is described in the class to which I just referred:

class ColorLite(SoCMini):

The author is not inherited from SoCCore, but from SoCMini. Are we rewriting everything? First let's take a look around. Where are these things described? We look around in the inclusion list... We don’t see any SoCMini there, but we see:

from litex.soc.integration.soc_core import *

We are already literate and know how to decode these lines. Or rather, pull out the path to the file from them. Let's go to the file \litex\soc\integration\soc_core.py and find out that SoCMini is described like this:

class SoCMini(SoCCore): def __init__(self, *args, **kwargs): if "cpu_type" not in kwargs.keys(): kwargs["cpu_type"] = "None" if "integrated_sram_size" not in kwargs.keys (): kwargs["integrated_sram_size"] = 0 if "with_uart" not in kwargs.keys(): kwargs["with_uart"] = False if "with_timer" not in kwargs.keys(): kwargs["with_timer"] = False SoCCore.__init__(self, *args, **kwargs)

It is completely inherited from SoCCore, it simply overlaps several arguments. To be honest, I acted further on a whim. I found these lines:

def soc_core_args(parser): … parser.add_argument(“—cpu-type”, default=None, help=”Select CPU: {}, (default=vexriscv)..” format(“, “.join(iter(cpu .CPUS.keys())))) parser.add_argument(“—cpu-variant”, default=None, help=”CPU variant (default=standard)”)

I found out by tracing that the cpu and cpu_type are in fact not equal to None , but should be... And therefore I added them to the arguments

cpu_type = None, cpu = None,

It helped. But it works - don’t touch it. This is how I output the lines that are needed. If necessary, you can follow the same path so as not to remember all the constants.

Hooray! The system has been created!

But there is little use for it yet. Let's add our Verilog module to the system. As I already noted, we will take the main files and ideas from here:

fomu litex vga (github.com)

Proplex windows technical specifications

PROPLEX is the first Russian developer and largest manufacturer of PVC window systems using Austrian technologies. The plant for the production of PVC window profiles and window sills was built in 1999 in the Moscow region by a team that stood at the origins of the Russian window industry. The enterprise is equipped with modern equipment from engineering companies from Austria and Germany. PROPLEX pays special attention to the selection of raw materials and components, using materials from leading suppliers from Austria, Germany, France, Russia and the USA in production.

PROPLEX Optima | System 58mm

PROPLEX-Optima is a system of high-quality three-chamber PVC profiles for the production of window structures.

The design of the PROPLEX™ PVC profile system is quite simple and technologically advanced and allows the production of windows of any shape. PROPLEX™ windows installed in an apartment, office or country house will provide an excellent level of comfort, protect against excessive noise and allow significant savings in energy consumption.

Specifications:

- Number of cameras in profile - 3

- System width, mm - 58

- Reduced heat transfer resistance of the profile, m2*S/W - 0.75 (0.64)

- Reduced heat transfer resistance of the window, m2*S/W - 0.75

- Double-glazed window width, mm - 4-34

- Fittings system - 12/20-9

- Profile durability, standard years - 60

Information from the official PROPLEX website

PROPLEX Balcony | System 46mm

The PROPLEX-BALCONY system is designed for glazing:

- balconies and loggias of residential buildings;

- summer houses;

- non-residential buildings;

- production premises.

The two-chamber profile in terms of heat transfer resistance (0.405 m2 0C/W) and strength of corner welded joints (frame - 1000N, sash - 1350N) meets the requirements of GOST 30673-99 and SNiP 02/23/2003 for translucent enclosing structures (Test report No. 27- 11/051/1 dated December 23, 2005).

In addition to the obvious price advantage, the PROPLEX-BALCONY system has a number of advantageous distinctive features from PVC and aluminum systems used for balcony glazing:

- Compared to aluminum profiles, products made from PVC profiles retain heat better;

- Compared to aluminum profiles, PVC profile products provide better sound insulation;

- Compared to sliding aluminum profiles, products made from PVC profiles provide better tightness and guarantee no blowing;

- PVC profiles, which are less aluminum, are susceptible to mechanical damage (scratches) both during processing, transportation, installation, and during subsequent everyday use;

- Almost the same range of components is used in production as in the manufacture of windows from the PROPLEX-Optima system. This minimizes the company's inventory and purchasing costs;

- the presence of additional profiles allows for glazing of objects with complex geometry;

- the PROPLEX-BALCONY system uses standard 12/20-9 fittings;

- to work with the PROPLEX-BALCONY system, it is enough to purchase an additional set of equipment;

- possibility of installing double-glazed windows;

Specifications:

- Number of cameras in profile - 3

- System width, mm - 46

- Reduced heat transfer resistance of the profile, m2*S/W - 0.55 (0.45)

- Reduced heat transfer resistance of the window, m2*C/W - 0.63

- Double-glazed window width, mm - 4-24

- Fittings system - 12/20-9

- Profile durability, standard years - 60

Information from the official PROPLEX website

PROPLEX Comfort | System 70mm

We present to your attention the 4-chamber PROPLEX-Comfort system, which is a logical development of the PROPLEX line of profile systems and created in full compliance with modern requirements for the quality of window profiles. Now you can choose from 2, 3, 4 and 5 chamber profile systems under our brand, each of which has a number of specific advantages and carries a specific functional load.

Quality characteristics:

- For all PROPLEX profile systems, including PROPLEX-Comfort, a mixture composition developed specifically for Russia is used.

- PROPLEX profiles are recognized as frost-resistant profiles and are recommended for installation in any climatic zones of Russia, including in the Far North;

- an installation depth of 70 mm provides an increased level of thermal protection and allows customers to significantly save on heating in winter, which becomes especially important for houses (premises) with an autonomous heating system;

- the milky white color of PROPLEX profiles belongs to a warm palette and creates a feeling of psychological comfort in the room;

- windows from the PROPLEX profile are recommended for installation in children's, preschool and medical institutions (appendix to the certificate of conformity No. ROSS RU.SL08.N00097 FROM 12/15/05);

- Compared to three-chamber profiles, windows from the Comfort series profile provide better heat and noise protection, and compared to five-chamber profiles - a better price.

Related article: Monolithic lintels over windows

Specifications:

- installation depth - 70mm;

- filling thickness -12: 40 mm;

- fittings system -12/20-9;

- design class (according to GOST 30673-99) - four-chamber;

- class for the thickness of the front walls (according to GOST 30673-99) - A, B;

- class for resistance to climatic influences (according to GOST 30673-99) - frost-resistant design;

- class for reduced heat transfer resistance (according to GOST 30673-99) - 2;

- heat transfer resistance 0.79 m2*C/W.

Information from the official PROPLEX website

PROPLEX Comfort Plus | System 70mm

We present to your attention the 4 (5) chamber system PROPLEX-Comfort Plus, which is a logical development of the line of PROPLEX profile systems and created in full compliance with modern requirements for the quality of window profiles. Now there is a choice among 2, 3, 4 and 5 chamber profile systems under the PROPLEX brand, each of which has a number of specific advantages and carries a specific functional load.

Specifications:

- Number of cameras in profile - 4.5

- System width, mm - 70, 88

- Reduced heat transfer resistance of the profile, m2*S/W - 0.79 (0.70)

- Reduced heat transfer resistance of the window, m2*C/W - 0.83

- Double-glazed window width, mm — 22-52

- Fittings system - 12/20-13

- Profile durability, standard years - 60

Information from the official PROPLEX website

PROPLEX Comfort Premium | System 70mm

PROPLEX-Premium is a system of high-quality five-chamber PVC profiles for the production of window structures.

Design features of the PROPLEX-Premium profile:

- The increased coefficient of resistance to thermal conductivity is achieved thanks to the five-chamber design and the profile width increased to 70 mm. And also by the fact that the reinforcing profile is separated from the outer front wall by at least two preliminary chambers, and from the inner front wall by 1-2 chambers, which reduces the likelihood of the formation of cold bridges and thereby increases the overall coefficient of thermal conductivity resistance. The increased width of the glass rebate allows the use of the entire range of double-glazed windows, including frost-resistant ones, up to 40 mm thick.

- The fold under the glass unit has a slight slope to free the cavity from condensation. When installing the filling into the rebate, a compensation spacer is installed under the glass unit, distributing the load on the rebate, on which, in turn, spacer adjusting spacers are installed.

- Internal partitions form a chamber under the reinforcing profile. To simplify the orientation of the reinforcing profile, as well as to form an air gap inside the chamber, additional bosses are provided on which the reinforcing profile rests.

- The PROPLEX-Premium profile system uses only two types of standard configuration reinforcing profiles. Reinforcing profiles for the frame and impost are made in the form of a rectangular pipe.

- On the hidden surfaces of the profile there are technological recesses (“grooves”) to facilitate the installation of fittings and reinforcing profiles. The use of “recesses” reduces the possibility of “turning” the screws, accurately marking the attachment points.

- The design of profiles of the PROPLEX-Premium system uses “booms” to ensure more reliable fastening of self-tapping screws in the profile body by increasing their contact area. When installing hinges on the sash profile, fastening with self-tapping screws is carried out through one front and two inner walls.

- Calculation of technological dimensions is carried out using the same formulas as when calculating a standard system. There is no need to make changes to the calculation methodology.

Specifications:

- Number of cameras in profile - 5

- System width, mm - 70

- Reduced heat transfer resistance of the profile, m2*C/W - 0.84 (0.76)

- Reduced heat transfer resistance of the window, m2*C/W - 0.81

- Double-glazed window width, mm — 12-42

- Fittings system - 12/20-19

- Profile durability, standard years - 60

Information from the official PROPLEX website

PROPLEX Optima (door system) | System 58mm

PROPLEX-Optima is a system of high-quality three-chamber PVC profiles for the production of window structures.

The design of the PROPLEX™ PVC profile system is quite simple and technologically advanced and allows the production of windows of any shape. PROPLEX™ windows installed in an apartment, office or country house will provide an excellent level of comfort, protect against excessive noise and allow significant savings in energy consumption.

Adding your module on Verilog

We copy the files gpu.v and hvsync_generator.v to the same place where our created Python script lives. We have to connect to this Verilog module:

module gpu(clk, hsync, vsync, color, x0, x1, y0, y1); input clk; output hsync, vsync; output color; wire pclk; wire display_on; wire signed [15:0] hpos; wire signed [15:0] vpos; input signed [15:0] x0; input signed [15:0] x1; input signed [15:0] y0; input signed [15:0] y1;

As you can see, we have to:

- Connect to the clock line from the clock domain,

- Forward the hsync , vsync and color to the pins of the chip,

- Apply signals from the Control/Status registers (that is, from the CSR module) to lines x0, x1, y0 and y1.

True, we won’t learn to read the status today, but everything has its time. The article is already huge, we should at least master something. Also, due to the enormity of the article, we will now make everything extremely simple. We will learn how to make it look better later, if the topic is in demand at all. If it doesn’t, then there will still be no point in describing it.

So. Open the example workshop_vga.py and transfer the class from there to us, above the main :

from litex.soc.interconnect.csr import AutoCSR, CSRStatus, CSRStorage class GPU(Module, AutoCSR): def __init__(self, pins, clk): self.x0 = CSRStorage(16, reset=100) self.x1 = CSRStorage( 16, reset=150) self.y0 = CSRStorage(16, reset=100) self.y1 = CSRStorage(16, reset=200) self.comb += [ pins[1].eq(0), ] self.specials += Instance( 'gpu', i_clk=clk, i_x0=self.x0.storage, i_x1=self.x1.storage, i_y0=self.y0.storage, i_y1=self.y1.storage, o_hsync=pins[2] , o_vsync=pins[3], o_color=pins[0] )

I specifically added an import line just before the class. As everyone has already guessed, I first added the class, then tried to run the script, and then I realized what was missing.

The GPU class inherits not only from Module, but also from AutoCSR. This class allows us to generate command and status registers by mapping them to the address space of the bus (in our case, the Wishbone bus). We've added four 16-bit registers. We also take the contents of a certain... Oh, I’m not good at Python terminology... A list, right? In this list we provide information about the chip pins used.

We try to start, make sure that everything comes together without errors.

Adding information about the pins of the microcircuit

And now we will take a step, the idea for which I spotted in a project that for some reason does not contain any links within itself and is not searched by Google. Therefore, I note that I did not write it myself, but I don’t remember where I found it. There is such a useful description of the gpio legs with a link to the connectors. As I already said, the FPGA legs with the connector contacts can be different. By specifying the board version in the options, we will always be sure that the system will select the correct FPGA legs for us! Despite all the shortcomings of Litex, this cannot be taken away from it! This system will take care of us! We place the text at the beginning of our file (but after the import lines). I will give only the key fragment. The rest can be seen in the full project (and if we remove the ellipsis, then this will be enough for our today’s tasks):

_gpios = [ # Attn. Jx/pin descriptions are 1-based, but zero based defs. used! # J1 ("gpio", 0, Pins ("j1:0"), IOStandard ("LVCMOS33")), # Input now ("gpio", 1, Pins ("j1:1"), IOStandard ("LVCMOS33" )), # Input now (“gpio”, 2, Pins(“j1:2”), IOStandard(“LVCMOS33”)), # Input now # GND (“gpio”, 3, Pins(“j1:4”) , IOStandard("LVCMOS33")), # Input now("gpio", 4, Pins("j1:5"), IOStandard("LVCMOS33")), # Input now("gpio", 5, Pins("j1 :6"), IOStandard("LVCMOS33")), # Input now("gpio", 6, Pins("j1:7"), IOStandard("LVCMOS33")), ("gpio", 7, Pins(" j1:8"), IOStandard("LVCMOS33")), ("gpio", 8, Pins("j1:9"), IOStandard("LVCMOS33")), ("gpio", 9, Pins("j1: 10"), IOStandard("LVCMOS33")), ("gpio", 10, Pins("j1:11"), IOStandard("LVCMOS33")), ("gpio", 11, Pins("j1:12" ), IOStandard("LVCMOS33")), ("gpio", 12, Pins("j1:13"), IOStandard("LVCMOS33")), ("gpio", 13, Pins("j1:14"), IOStandard("LVCMOS33")), # GND # J2("gpio", 14, Pins("j2:0"), IOStandard("LVCMOS33")), # Input now("gpio", 15, Pins("j2 :1"), IOStandard("LVCMOS33")), # Input now...("gpio", 111, Pins("j8:14"), IOStandard("LVCMOS33")), # GND ]

PROPLEX-Comfort profile

The 4-chamber PROPLEX-Comfort system is a logical development of the Proplex profile systems. It was created taking into account all modern requirements for the quality of window profiles.

Main technical characteristics of Proplex-Comfort:

- installation depth - 70mm;

- filling thickness -12: 40 mm;

- fittings system -12/20-9;

- design class (according to GOST 30673-99) - four-chamber;

- class for the thickness of the front walls (according to GOST 30673-99) - B;

- class for resistance to climatic influences (according to GOST 30673-99) - frost-resistant design;

- class for reduced heat transfer resistance (according to GOST 30673-99) - 2;

- heat transfer resistance 0.79 m2*C/W.

We form the required block in the system

So. Verilog files for inclusion have been copied, the wrapper class has been created, and the gpio legs have been described. The infrastructure is ready! Let's start implementation! We will implement between the announcement of our SoC system and its construction:

Adding a list of used legs:

soc.platform.add_extension(_gpios) # General LED outputs touch_pins = [ soc.platform.request("gpio", 0), soc.platform.request("gpio", 1), soc.platform.request("gpio" , 2), soc.platform.request("gpio", 3), soc.platform.request("gpio", 4) ]

We get a link (or whatever it’s called in Python) to the clock line. True, now the resulting frequency will not be exactly the one we need, but we will correct it in the next article, when we figure out what exactly we need. Everything is simple there, but you need to trace it a little.

clk = soc.crg.cd_sys.clk

That's all! And we insert our GPU module, and also implement its registers into the CSR block:

soc.submodules.gpu = GPU(touch_pins, clk) soc.add_csr("gpu")

Well, we also inform you that we need to take the Verilog files:

soc.platform.add_source("hvsync_generator.v") soc.platform.add_source("gpu.v")

In total, including the reference lines before and after, we get:

soc = BaseSoC(board=args.board, revision=args.revision, sys_clk_freq = int(float(args.sys_clk_freq)), with_ethernet = args.with_ethernet, with_etherbone = args.with_etherbone, eth_ip = args.eth_ip, eth_phy = args. eth_phy, use_internal_osc = args.use_internal_osc, sdram_rate = args.sdram_rate, cpu_type = None, cpu = None, **soc_core_argdict(args) ) soc.platform.add_extension(_gpios) # General LED outputs touch_pins = [ soc.platform.request( "gpio", 0), soc.platform.request("gpio", 1), soc.platform.request("gpio", 2), soc.platform.request("gpio", 3), soc.platform. request("gpio", 4) ] clk = soc.crg.cd_sys.clk soc.submodules.gpu = GPU(touch_pins, clk) soc.add_csr("gpu") soc.platform.add_source("hvsync_generator.v") soc.platform.add_source("gpu.v") builder = Builder(soc, **builder_argdict(args)) builder.build(**trellis_argdict(args), run=args.build)